Effects of Package Level Structure and Material Properties on Solder Joint Reliability Under21,, T7/0.TE.54i2.7(L)8.5 [(52) JESD22-B111 is conducted to obtain the con mode, rate, location, and the corresponding bo accelerations. Finite scale in cining transportation or customer usage may accelerations. Finite scale in cining transportation or customer usage may be accelerated as a few delivers of the cining transportation or customer usage may be accelerated as a few delivers of the cining transportation or customer usage may be accelerated as a few delivers of the cining transportation or customer usage may be accelerated as a few delivers of the cining transportation or customer usage. against the experimentations. Three primary failure modes are BC compliance of the templastic drop the crack of pad crater in printed circuit board on pad crater in printed circuit board on page 1. istress buffer mechanisms, such as incorner incorner in large in large in the large stresses. For a competitation of the acur pad trater) provide a competitation of the acur pad trater) provide a competitation of the acur pad trater) provide a competition of the acur pad trater pad trat which encapsulated predoctory by the failure indicated right ground test fives as for solder joint stress a multichannel real-time monitoring system had been amic prehensive data from Astmulation and interxeportimen the high speed cameras has also been developed to acquire that package structures and rematerial modeling techniques have placed in the package structures and the package structures are structures and the package s Irole on the dynamic responses of solder joints.

C<sub>BGA packages</sub>, **joint reliability performance** of a CS BGA of are defined for the package/die size ratio less than 1.2. Conventional (factor pend Son but the the are still on the uneut wafer. There have been a variety of WEP technologies with distinct package structures. Standard ball on I/O WLP has evolved with the Incorporation of redistribution.

layer (RDL) process, copper post process, and compliant layer

Ball grid array (BGA),

process [2], [3].

dynamics, finite element analysis (FEA), impact

B111, reliability, solder joints, wafer level pa

publication December 11, 2012; date of current version January 4, 2013. Recommended for publication by Associate Editor I. C. Ume upon evaluation of reviewers' comments.

The authors are with the Department of Mechanical Engineering, Lamar University, Beaumont, TX 77710 USA (e-mail: xuejun.fan@lamar.edu; amarinder.s.me@gmail.com; harry2k23@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCPMT.2012.2217744

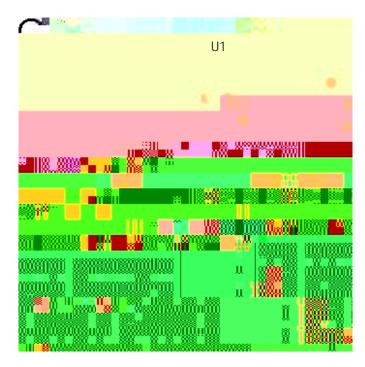

Fig. 4. Crack map of group A WLP after drop test (red areas correspond to solder joint IMC crack at package side).

1500-g peak and 0.5-ms duration, which can be described by equation as follows:

$$a = \begin{cases} 1500g \sin \frac{\pi t}{t_w}, & t & t_w, t_w = 0.5\\ 0, & t & t_w \end{cases}$$

(1)

where a is the acceleration of the drop table, g is acceleration due to gravity (9.8 m/s<sup>2</sup>), and  $t_w$  is the impulse duration (ms).

Strain gauge rosettes are used to measure board strain transient responses at various locations. The comparison between the strain measurement and finite element results will be discussed in Section V. Dye and pry techniques are applied for failure analysis for the selected components to determine the failure mode and crack propagation pattern. The dominant failure mode in this study was the solder joint crack at IMC layer on the component side. A typical failure map showing crack size and locations is illustrated in Fig. 4. It is seen that the solder joints at left and right columns show the most crack propagations compared to the other columns. In addition, the cracks initiate from solder joint inner side and propagate toward opposite side.

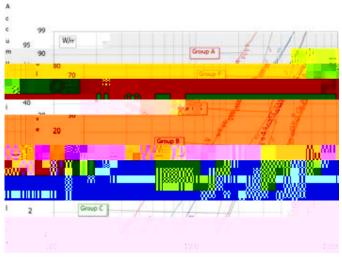

A typical Weibull plot for the failure rate of all six groups is shown in Fig. 5 for a  $6 \times 6$  mm WLP package. A total of ten test boards were tested to have sufficient failure data points for all groups. For the package size of  $6 \times 6$  mm, the failure rate rank is: A>F>E>B>D>C. It is seen that group A (corner components) has the greatest failure rate, followed by groups F and E (center row components). Groups B, C, and D have the smallest failure rates.

For various types of packages with various sizes, it is generally seen that the first resonant frequency of the test board is registered around 230 Hz, and the second one is found at approximately 650 Hz.

Fig. 5. Weibull plot of drop test failures for six component groups for a  $6\times 6$  mm copper post WLP.

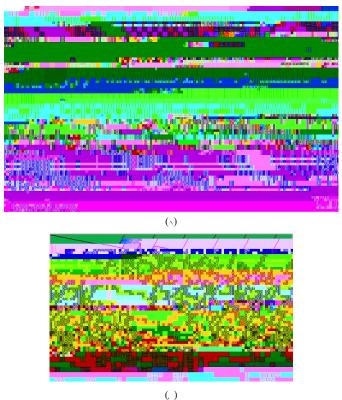

Fig. 6. Quarter global finite element model. (a) Global finite element model for board and (b) solder joint finite element mesh in global model.

## IV. MATHEMATICAL FORMULATIONS AND FINITE ELEMENT MODELS

For JESD22-B111 drop test, the main interest is the component dynamic responses, especially the solder joint transient stresses. In solving a dynamic problem, it is important to know whether the problem falls into the category of wave propagation or structural transient dynamic response. It may be

Fig. 7. Local finite element model. (a) Overall local model. (b) Details of solder joint finite element model. (c) Cross-section of refined meshes of corner joints. (d) IMC layer finite element mesh.

helpful to compare the time scale of stress wave propagation in PCB to a typical impulse scale (0.5 ms per JEDEC definition) and PCB dimension. The speed of stress wave is  $\overline{\mu/\rho}$ , where  $\mu$  and  $\rho$  are shear modulus and density of the board. The value is approximately  $7\times10^3$  mm/ms, which means that the stress wave has already traveled back and forth in PCB (130-mm length) several times within 0.5 ms to reach an equilibrium of being bulk structural dynamic responses. Therefore, the problem under study is solved by structural dynamics.

For the loading condition described in (1), the load in terms of acceleration on mounting screws can be converted to body TABLE II

failure. A tradeoff design must be considered in the selection of compliant layer material, such as wafer level epoxy in copper post WLP.

## D. Resultant Effects

To compare solder joint performance in a BGA package

- [16] L. X. Shen, "Simulation of drop test board with 15 components using explicit and implicit solvers," in *Proc. Int. ANSYS Conf.*, Pittsburgh, PA, 2008

- [17] H. S. Dhiman, "Study on finite element modeling of dynamic behaviors of wafer level packages under impact loading," M.S. thesis, Dept. Electr. Eng., Lamar Univ., Beaumont, TX, 2008.

- [18] H. S. Dhiman, X. J. Fan, and T. Zhou, "Modeling techniques for board level drop test for a wafer-level package," in *Proc. Int. Conf. Electron. Packag. Technol. High Density Packag. (ICEPT-HDP)*, 2008, pp. 1–8.

- [19] A. S. Ranouta, "Effects of orientation, layout, component structure and geometry on drop reliability of chip scale packages," M.S. thesis, Dept.